# EGC220 Class Notes 4/11/2023

#### **Baback Izadi**

Division of Engineering Programs bai@engr.newpaltz.edu

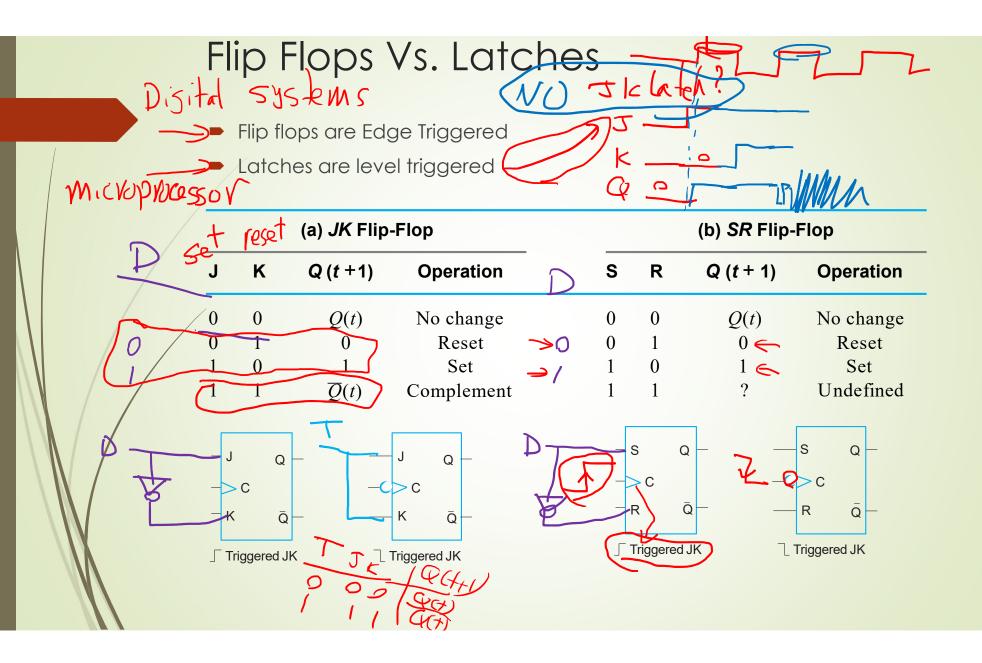

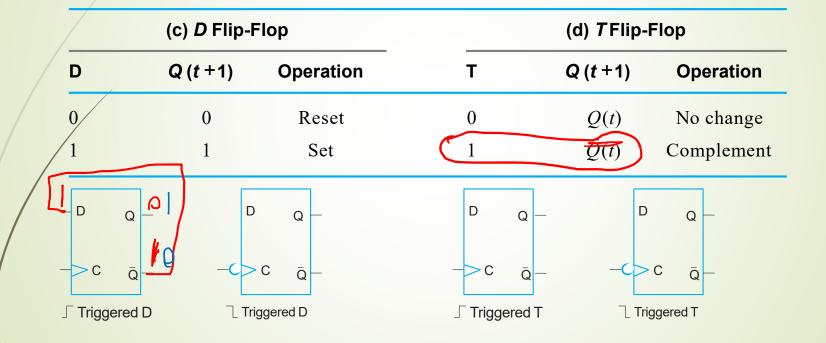

## Flip Flops Vs. Latches

S P

- Flip flops are Edge Triggered

- Latches are level triggered

### Problem 1

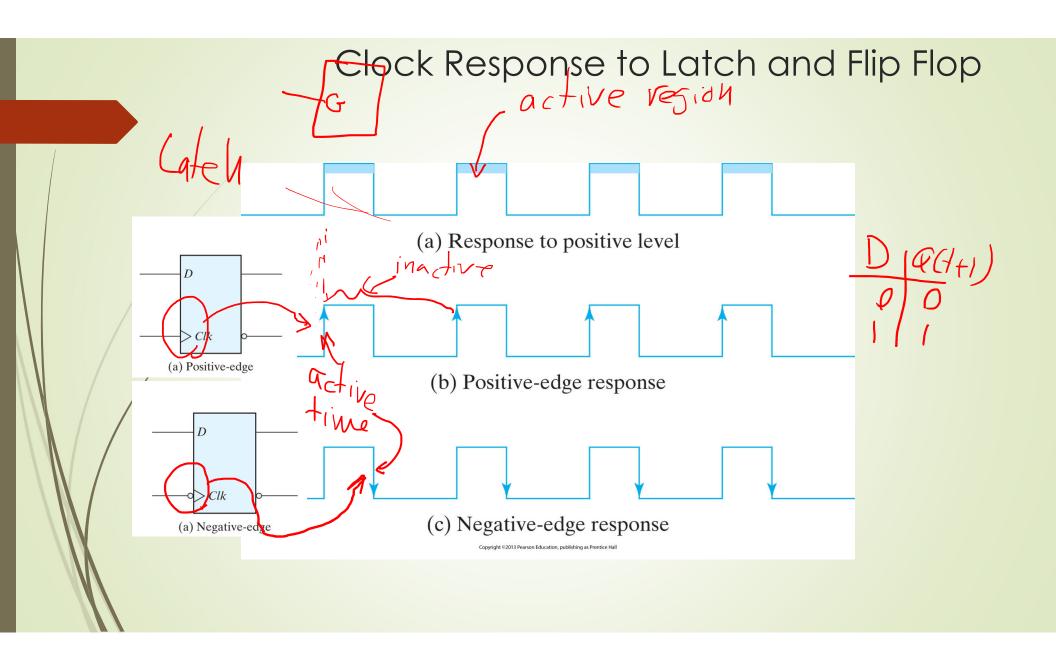

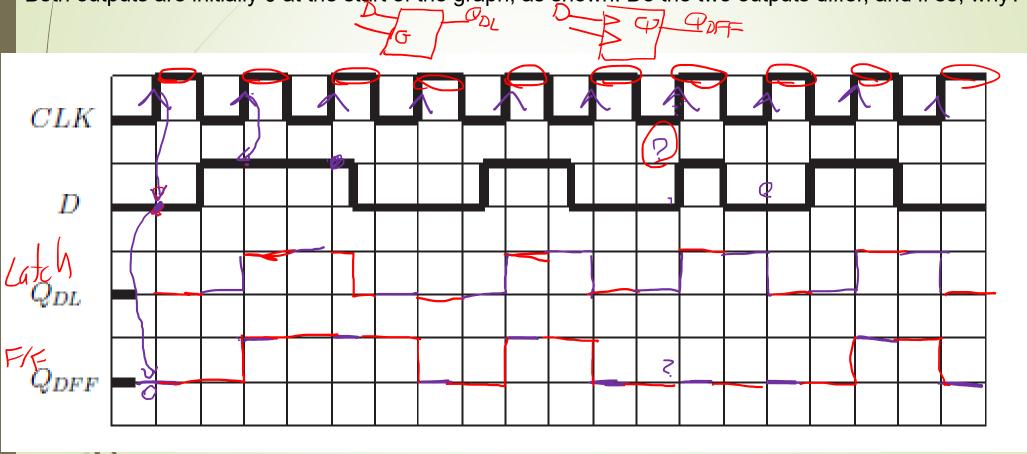

On the following graph, inputs CLK and D are shown. They are inputs to both a D latch and a D flip-flop. CLK goes into the active high G input of the D latch and positive edge clock input of the D flip-flop. Show the output of the D latch as  $Q_{DL}$  on the graph and the output of the D flip-flop as  $Q_{DFF}$  on the graph. Both outputs are initially 0 at the start of the graph, as shown. Do the two outputs differ, and if so, why?

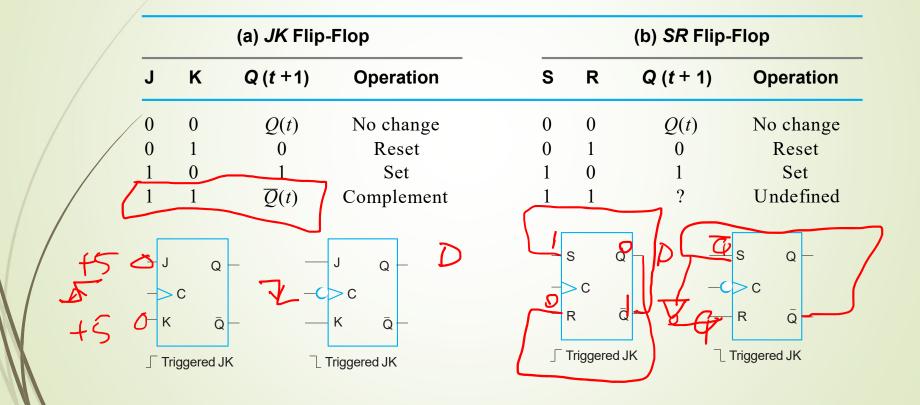

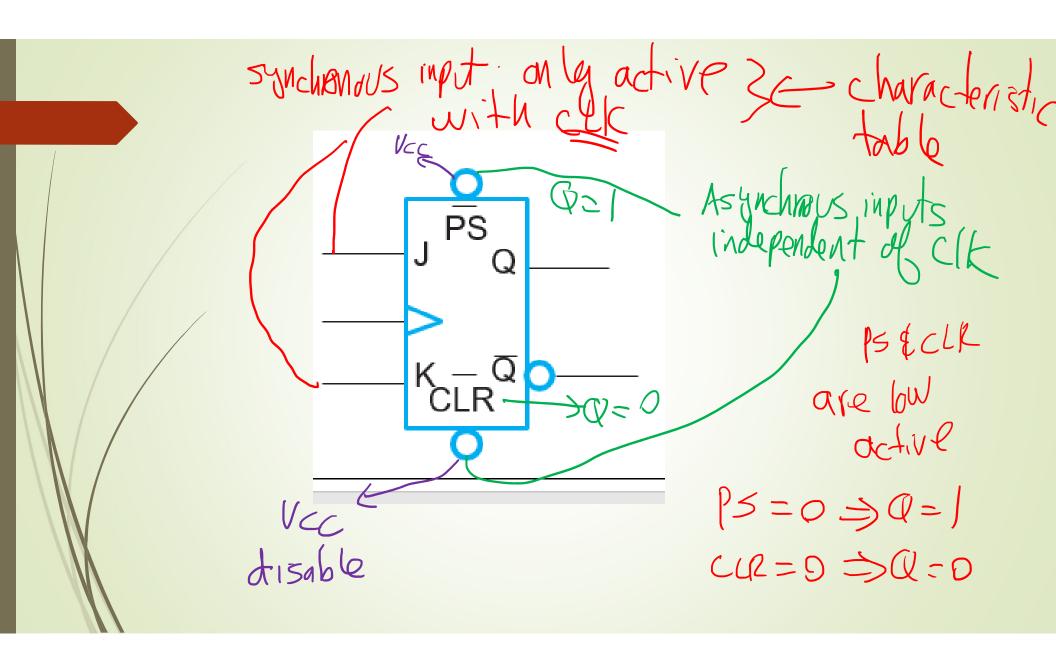

Problem 2. Complete the following timing diagram for a JK flip-flop with a low active preset (PS) and clear (CLR). 0 CLR

## Flip Flops Vs. Latches

- Flip flops are Edge Triggered

- Latches are level triggered

## Flip Flops Vs. Latches

- Flip flops are Edge Triggered

- Latches are level triggered